Layout vs Schematic Debug (LVS)

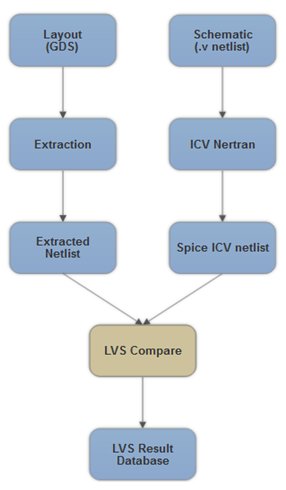

Input files for LVS in ICV tool are listed below:

- GDS (layout stream file): It is used by the LVS tool to generate layout netlist by extraction, which is used for LVS comparison.

- Schematic netlist: It is used as a source netlist for LVS comparison.

- Rule deck file: Rule deck file consists of required instructions and files to guide tool for performing LVS. This rule deck file also contains a layer definition, which is useful for extraction.

- Equivalence file: It is used by the tool for ICV LVS comparison and it consists of cell pairs, which is made-up of one from the layout netlist and another from the schematic netlist.

ICV has nettran utility for translation of input verilog netlist to ICV schematic netlist, which is further useful for comparison purpose.

All devices and connections between them are extracted from GDS in the layout extraction step. The tool also generates an equivalence point file after the extraction for comparison of layout and schematic. This equivalence file is useful for comparison.

In comparison step, tool does the comparison in the following way: Tool compares the number of devices in schematic and in layout, the number of nets in schematic and in layout, types of device in schematic and in layout, and then generates the result reports. Error report contains a list of incorrect devices, incorrect nets, which is useful to debug the LVS issue.

Common LVS issues and their debug

- Open

- Shorts

- Missing components

- Missing global net connect

Open: Shapes of the nets having the same layout text on them are not intersecting or touching causes opens in design. Opens in the design are responsible for floating connections in the design. This floating connection will cause major defects in chips. So, it is very important to find opens in the design. Running open finding utility of PnR tool before running LVS, is helpful in the early design phase.

This type of issue can be solved by connecting layout shapes of single net that is left open.

Short: If layers in layout having different layout text on them are overlapping or intersecting, it will result in short in the design. Presence of the short in design will cause chip failure.

Short can be resolved by properly rerouting the net.

Internal shorts with Macros: In a design, due to the complexity of the design or due to incorrect settings, it can happen that the PnR tool routes nets in a way that creates short with the internal geometries of the macros. It can also happen if routing blockage is missing in LEF of the macro. Sometimes while doing manual custom routing, short is created between custom route and the internal routing of the macro. This short is not easily reported in the PnR tool environment. When we merge the GDS of the hard macro with the top-level block, the short is visible in the GDS. This short can be debugged using VUE utility of ICV. Below is a snippet that shows how a signal net is incorrectly routed over the hard macro. The layer is blocked over the macro, as internal geometries of the hard macro is present. This net will cause a short with the internal geometries of the macro.

PG short with signal net: When there is a PG short in the design, it is very difficult to identify it. PG short can be a short between a power net and a ground net or it can be a short between a power/ground net and a signal net. When a PG net is shorting with fairly long signal net and since the PG net is connected to so many devices, it is very difficult to pin-point a short location. To debug this issue, there is a way in ICV to add a text on the signal net which is shorting with PG net.

Missing components: If some of the spice file or GDS file is missing while merging database, it shows missing components error. For example: if you have cell ABC used in the design, but not defined in GDS list or spice list to be used for LVS flow, it can cause missing components error. Either the list needs to be modified or ABC cell needs to be excluded from the LVS comparison (this depends on the functionality of the cell, only physical cells may be excluded in the comparison).

Missing global net connect: If PG pins of the cells is not connected to any power/ground net using connect_pg_net commands, it causes device mismatches and LVS errors for most of the design. For example, even if the standard cell PG pin name is VDD, tool does not connect it to VDD net of design. We need to use below command to connect such pins.

connect_pg_net -net VDD [get_pins -hierarchical */VDD]

Conclusion:

LVS is useful technique to verify the correctness of the physical implementation of the netlist. open, shorts, missing components, and missing global net connect are potential issues that can affect the functionality of design and may not be detected at early implementation stage, so LVS is useful to report these issues in design. Once these issues are reported by Physical verification tool, it can be solved by various techniques as discussed in this article.